#### **Copyright Notice**

This document is copyrighted, 2002. All rights are reserved. The original manufacturer reserves the right to make improvements to the products described in this manual at any time without notice.

No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of the original manufacturer. Information provided in this manual is intended to be accurate and reliable. However, the original manufacturer assumes no responsibility for its use, nor for any infringements upon the rights of third parties which may result from its use.

#### Acknowledgments

PC-LabCard is a trademark of Advantech Co., Ltd. IBM and PC are trademarks of International Business Machines Corporation. MS-DOS, Windows® Microsoft® Visual C++ and Visual BASIC are trademarks of Microsoft® Corporation. Intel® and Pentium® are trademarks of Intel Corporation. Delphi and C++ Builder are trademarks of Inprise Corporation.

#### **CE** notification

The MIC-3620, developed by ADVANTECH CO., LTD., has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **On-line Technical Support**

For technical support and service, please visit our support website at:

http://www.advantech.com/support

# **Contents**

| INTR  | DDUCTION                 | 1  |

|-------|--------------------------|----|

|       |                          |    |

| 1.1   | NTRODUCTION              | 2  |

| 1.2   | FEATURES                 | 2  |

| 1.3   | SPECIFICATIONS           | 3  |

| HARD  | WARE CONFIGURATION       | 5  |

| 2.1   | NITIAL INSPECTION        | 6  |

|       | HARDWARE INSTALLATION    |    |

| 2.3   | BOARD LAYOUT: DIMENSIONS | 9  |

|       | SSIGNMENT & WIRING       |    |

| 3.1   | PIN ASSIGNMENTS          | 12 |

| REGIS | STER STRUCTURE & FORMAT  | 15 |

| 4.1   | REGISTER STRUCTURE       | 16 |

# Chapter

# 1.1 Introduction

The MIC-3620 is a 3U-sized 8-port High Speed RS-232 PCI Comm. CompactPCI<sup>TM</sup> and serial communication card, which complies with PICMG 2.0 R2.1 CompactPCI specifications. The MIC-3620 requires only one CPCI slot within the computer and provides independent serial channels. All channels are addressed in a continuous 32 byte I/O block for simplified software access. It is possible for all channels to share one PCI interrupt. An interrupt status register is available for determining the interrupt source.

The MIC-3620 comes standard with 16C954 UARTs containing an optional 128 byte FIFOs. These upgraded FIFOs greatly reduce CPU overhead and are an ideal choice for heavy multitasking environments.

# 1.2 Features

- PCI Specification 2.1x compliant

- Speeds up to 921.6 Kbps

- 16C954 UARTs with 128-byte FIFO standard

- Standard Industrial CPCI Board size

- I/O address automatically assigned by PCI Plug-and-Play

- OS supported: Windows 98, Windows NT, Windows 2000 and Windows XP

- Interrupt status register for increased performance

- Space reserved for termination resistors

# 1.3 Specifications

• Bus Interface: CPCI bus specification 2.1x compliant

• IRQ: all ports use the same IRQ assigned by PCI Plug-and-Play

• **Data bits:** 5, 6, 7, 8

• Stop bits: 1, 1.5, 2

• Parity: none, even, odd

• BUS controller: PCI9030

• **UART:** 2 x 16C954

• **Speed (bps):** 50 ~ 921.6 K

• Data signals:TxD, RxD, RTS, CTS, DTR, DSR, DCD, GND (for RS-232)

• Power consumption: +5V@2.0A(MAX), +3.3V@3A, +12V@1A

• **Dimensions:** 160 mm x 100 mm

• Operating temperature: 0'C~ 70'C (referring to IEC68-2-1, 2)

• Operating Humidity: 5 ~ 95% Relative Humidity,

non-condensing (referring to IEC 68-2-1, 2)

• Operating Humidity: 5 ~ 95% Relative Humidity,

non-condensing (referring to IEC 68-2-3)

• Storage Temperature: -20 ~ 80 'C

Chapter Chapter

**Hardware Configuration**

This chapter gives users a package item checklist, proper instructions about unpacking and step-by-step procedures for card installation.

# 2.1 Initial Inspection

In addition to this manual, you should find the following items inside the shipping package of the MIC-3620:

- CPCI communication interface card MIC-3620

- Advantech Automation Software CD-ROM

- CPCI communication card user's manual

- Wiring cable

Prior shipping, we have carefully inspected the CPCI communication card series. It should be free of marks and scratches and in perfect working order on receipt. As you unpack the CPCI communication card series, check for signs of shipping damage (damaged box, scratches, dents, etc.). If it is damaged or fails to meet specifications, immediately notify our service department or your local sales representative. Please also notify the carrier. Retain the shipping carton and packing materials for inspection by the carrier. Once inspected, we will make arrangements to repair or replace the unit.

When you handling the CPCI communication card series, remove its protective packaging by grasping the rear metal panel. Keep the anti-vibration packaging. Whenever you remove the card from the PC, store it in this package for protection.

#### Note:

Discharge your body's static electric charge by touching the back of the grounded chassis of the system unit (metal) before handling the board. You should avoid contact with materials that hold a static charge such as plastic, vinyl and styrofoam. Handle the board only by its edges to avoid static damage to its integrated circuits. Avoid touching the exposed circuit connectors. We also recommend that you use a grounded wrist strap and place the card on a static dissipative mat whenever you work with it.

# 2.2 Hardware Installation

#### Note

Make sure you have installed the driver first before you install the card (please refer to the software installation details in **Chapter 3** *Driver Setup & Installation*).

Once you have doubled check that the DLL driver of the MIC-3620 installation is complete, you can proceed with the MIC-3620 card installation in your CPCI computer. Once in doubt, please consult with your computer's user manual or related documentation. Please follow the following steps to install the card on your system.

#### To install a card:

- **Step 1:** Remove one cover on the unused slot of your CPCI computer slot.

- **Step 2:** Hold the Card Vertically. Be sure that the card is pointing in the correct direction. The components of the card should be pointing to the right-hand side and the black handle of the card should be pointing to the lower edge of the chassis.

- Step 3: Hold the lower handle and pull the handle down to unlock it.

- **Step 4:** Insert the MIC-3620 card into the CPCI chassis carefully by sliding the lower edges of the card into the card guides.

- **Step 5:** Gently push the card into the slot by sliding the card along the card guide until J1 meets the long needle on the backplane.

#### Note

If your card is correctly positioned and has slid all the way into the chassis, the handle should match the rectangular holes. If not, remove the card from the card guide and repeat step 3 again. Do not try to install a card by forcing it into the chassis.

**Step 6:** Push the card into the right place, secure the card by pushing the handle to lock it into place.

# Note 1

Advantech MIC-3612's "Hot-Swap" function complies with CPCI Hot Swap Specification PICMG 2.1 R2.0.

#### Note 2

Because the card holds "Hot-Swap", **Blue LED** on the front plane indicates the status of the card installation when the system is on. In **step 5**, **Blue LED** will turn on when J1 meets the long needle on the backplane; In **step 6**, the system will automatically configure the card, the **Blue LED** will turn off when the system completes the device configuration.

If system's power is turned off, you can install the card step by step without considering the **Blue LED's** state.

# To remove a card:

- **Step 1:** Push the handle down to unlock the card, and the CPCI system will automatically uninstall the card configuration.

- **Step 2:** Once the system finishes the device configuration, the **Blue LED** on front plane will turn on. Now you can slide the card out.

# Note

Because the card holds "Hot-Swap", the above steps will remove the card process when the system is on. If the system power is off, please do **step1** and **step2** without attending **Blue LED's** state.

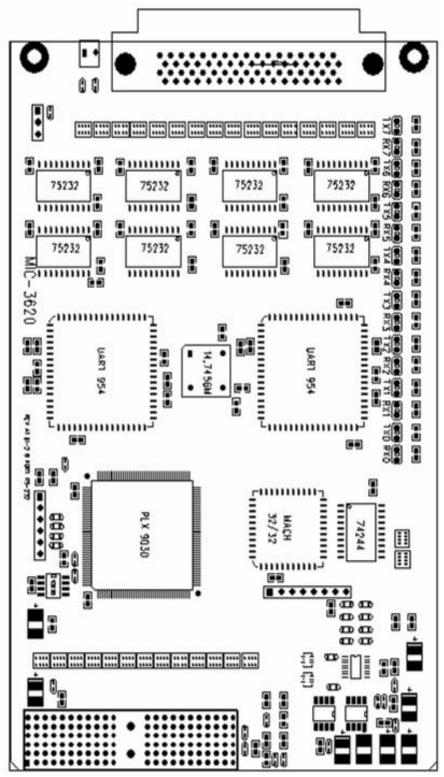

Figure 1-1: MIC-3620 board layout: Dimensions

#### **Connectors**

MIC-3620 has a 68-pin SCSI connectors.

Chapter 3

Pin Assignment & Wiring

# 3.1 Pin assignments

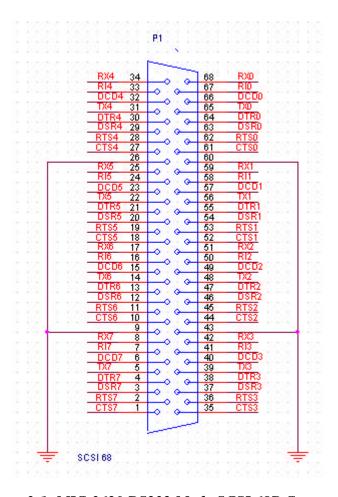

The MIC-3620 has RS-232 8-ports. The following lists the pin assignments of the SCSI68 connector on the bracket. You may fabricate octopus cable for SCSI68 to  $8 \times DB9$  with these output pin.

Pin No. Signal Pin No. Signal Pin No. Signal 65 TX0 64 DTR0 62 RTS0 RX0 63 DSR0 CTS0 68 61 66 DCD0 67 RI0 60 GND 56 TX1 55 DTR1 53 RTS1 59 RX1 54 DSR1 52 CTS1 DCD1 57 58 RI1 47 DTR2 48 TX2 45 RTS2 51 RX2 46 DSR2 44 CTS2 49 DCD2 50 RI2 43 **GND** 39 TX3 38 DTR3 36 RTS3 DSR3 CTS3 42 RX3 37 35 40 DCD3 41 RI3 31 TX4 30 DTR4 28 RTS4 RX4 29 DSR4 CTS4 34 27 32 DCD4 33 RI4 26 **GND** DTR5 RTS5 22 TX5 21 19 RX5 20 DSR5 18 CTS5 25 23 DCD5 24 RI5 13 RTS6 14 TX6 DTR6 11 17 RX6 12 DSR6 10 CTS6 15 DCD6 16 RI6 9 **GND** 5 TX7 4 DTR7 2 RTS7 RX7 3 DSR7 1 CTS7 8 6 DCD7 RI7

Table 3-1: MIC-3620 DB78P Connector Pin Assignment

Table 3-2 is DB9P Male Connector Description.

| Signal | Name                | Pin# | Mode   |

|--------|---------------------|------|--------|

| GND    | Ground              | 5    |        |

| TX     | Transmit Data       | 3    | Output |

| DTR    | Data Terminal Ready | 4    | Output |

| RTS    | Request To Send     | 7    | Output |

| RX     | Receive Data        | 2    | Input  |

| DSR    | Data Set Ready      | 6    | Input  |

| CTS    | Clear To Send       | 8    | Input  |

| DCD    | Data Carrier Detect | 1    | Input  |

| RI     | Ring Indicator      | 9    | Input  |

Table 3-2: DB9 Male Connector Description

The following diagrams show the pin assignments for the MIC-3620 SCSI  $68\ \mathrm{pin}$  connector.

Figure 3-1: MIC-3620 RS232 Mode SCSI 68P Connector

Chapter Chapter

Register structure & format

# 4.1 Register Structure

This appendix gives short descriptions of each of the module's registers. For more information please refer to the data book for the OX16C954 UART chip. All registers are one byte. Bit 0 is the least significant bit, and bit 7 is the most significant bit. The address of each register is specified as an offset from the port base address (BASE).

DLAB is the "Divisor Latch Access Bit", bit 7 of BASE+3.

BASE+0 Receiver buffer register when DLAB=0 and the operation is a read.

BASE+0 Transmitter holding register when DLAB=0 and the operation is a write.

BASE+0 Divisor latch bits 0 - 7 when DLAB=1.

BASE+1 Divisor latch bits 8 - 15 when DLAB=1

The two bytes BASE+0 and BASE+1 together form a 16-bit number, the divisor, which determines the baud rate together with the values of TCR and CPR and Bit7 of MCR (Modem Control Register) (refer to 16C954 datasheet). The formula to set BaudRate as follows:

$$BaudRate = \frac{InputClock}{SC*Divisor*prescaler}$$

In formula, SC is sample clock value defined by TCR, when TCR=0x00, SC =16.

**Prescaler** is defined by MCR[7] and CPR.

**Prescaler** = 1 when MCR[7] = '0';

**Prescaler** = M+(N/8), when MCR[7] = 1,

where: M = CPR[7:3] (Integer part – 1 to 31)

N = CPR[2:0] (Fractional part – 0.000 to 0.875)

While Bit7 of MCR is Logic"1", TCR=0x00 and CPR=0x40, set the divisor as follows:

| Baudrate | Divisor | Baudrate | Divisor |

|----------|---------|----------|---------|

| 50       | 2304    | 3600     | 32      |

| 75       | 1536    | 4800     | 24      |

| 150      | 768     | 7200     | 16      |

| 300      | 384     | 9600     | 12      |

| 600      | 192     | 19200    | 6       |

| 1200     | 96      | 38400    | 3       |

| 1800     | 64      | 57600    | 2       |

| 2400     | 48      | 115200   | 1       |

*Table 4-1*

Else, while Bit7 of MCR is Logic"0", TCR=0x00, set the divisor as follows:

| Baudrate | Divisor |

|----------|---------|

| 230400   | 4       |

| 307200   | 3       |

| 460800   | 2       |

| 921600   | 1       |

*Table 4-2*

**BASE+1** Interrupt Enable Register (IER) when DLAB=0

Bit0 Enable received-data-available interrupt

Bit1 Enable transmitter-holding-register-empty interrupt

Bit2 Enable receiver-line-status interrupt

Bit3 Enable modem-status interrupt

BASE+2 (read) Interrupt status register(ISR)

BASE+2 (write) FIFO Control Register (FCR)

Bit0 Enable transmit and receive FIFO

Bit1 Clear contents of receive FIFO

Bit2 Clear contents of transmit FIFO

Bits6-7 Set trigger level for receiver FIFO interrupt.

| Bit 7 | Bit 6 | FIFO Trigger Level |

|-------|-------|--------------------|

| 0     | 0     | 16                 |

| 0     | 1     | 32                 |

| 1     | 0     | 112                |

| 1     | 1     | 120                |

*Table 4-3*

#### **BASE+3** Line Control Register (LCR)

Bit 0 Word length select bit 0

Bit 1 Word length select bit 1

Bit 2 Number of stop bits

Bit 3 Parity enable

Bit 4 odd/even parity select

Bit 5 Force parity

Bit 6 Tx break

Bit 7 Divisor Latch Access Bit (DLAB)

| Bit 1 | Bit 0 | Word Length (bits)_ |

|-------|-------|---------------------|

| 0     | 0     | 5                   |

| 0     | 1     | 6                   |

| 1     | 0     | 7                   |

| 1     | 1     | 8                   |

*Table 4-4*

# **BASE+4** Modem Control Register (MCR)

Bit 0 DTR

Bit 1 RTS

Bit 3 Interrupt enable by software

Bit 7 Baud prescale select

# **BASE+5** Line Status Register (LSR)

Bit 0 Receiver data ready

Bit 1 Overrun error

Bit 2 Parity error

Bit 3 Framing error

Bit 4 Breaks interrupt

Bit 5 Transmitter holding register empty

Bit 6 Transmitter shift register empty

Bit 7 At least one parity error, framing error or break indication on FIFO

# **BASE+6** Modem Status Register (MSR)

Bit 0 Delta CTS

Bit 1 Delta DSR

Bit 2 Trailing edge ring indicator

Bit 3 Delta received line signal detect

Bit 4 CTS

Bit 5 DSR

Bit 6 RI

Bit 7 DCD

BASE+7 Temporary data register and indexed control Register offset value bits